référence

|

valeur

|

nombre

|

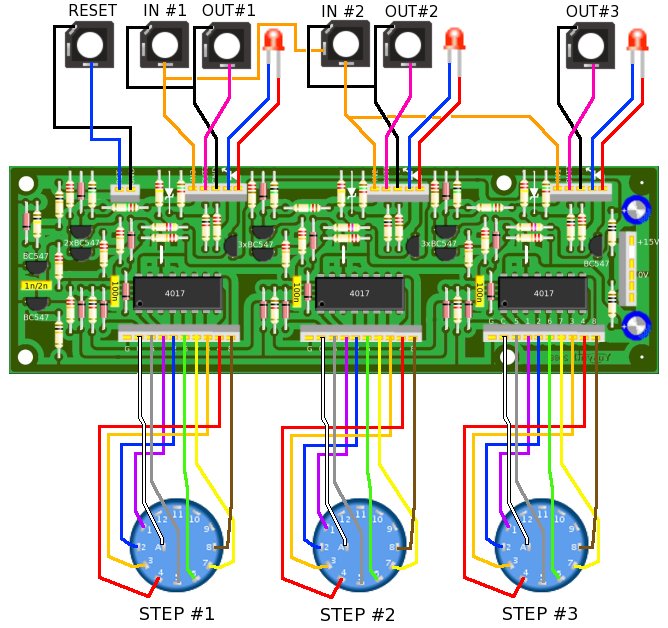

U1,U2,U3

|

4017 CMOS compteur

décimal

|

3

|

Q1.....Q11

|

BC547

|

11

|

D1.....D16

|

1N4148

|

16

|

Z1....Z3

|

zéner 5.1V

optionnelles

|

3

|

R1,R2

|

10 ohm 5% |

2

|

| R5,R12,R17,R24,R29,R36 |

220 ohm 5% |

6

|

| R8,R14,R20,R26,R32,R38 |

1K 5%

|

6

|

R13,R25,R37

|

1.5K 5% |

3

|

| R10,R22,R34 |

4.7K 5% |

3

|

| R41 |

10K 5%

|

1

|

R6,R7,R9,R18,R19,R21,R30,R31,R33,R42,

R43

|

22K 5% |

11

|

| R39 |

100K 5%

|

1

|

| R11,R23,R35 |

220K 5% |

3

|

| R3,R15,R27,R40 |

1M 5% |

4

|

R4,R16,R28

|

1.2M 5% |

3

|

C6

|

1nF to 2.2nF polyester

|

1

|

C3,C4,C5

|

100nF céramique

multicouche

|

3

|

C1,C2

|

22µF/25V

electrochimique

|

2

|

LD1,LD2,LD3

|

DEL rouge

|

3

|

Jk1...Jk6

|

socle jack 6.5 mm

|

6

|

|