| Update : jan. 31st, 2009 |

Envelope generator

ADSR |

|

back to summary |

|

|

| Description |

| Update : jan. 31st, 2009 |

Envelope generator

ADSR |

|

back to summary |

|

|

| Description |

|

|

|

Schematic |

|

|

| How does it work ? |

|

|

||

|

||

|

||

|

||

|

||

|

|

|

|

|

Components and building guide

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| R3 is missing... |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

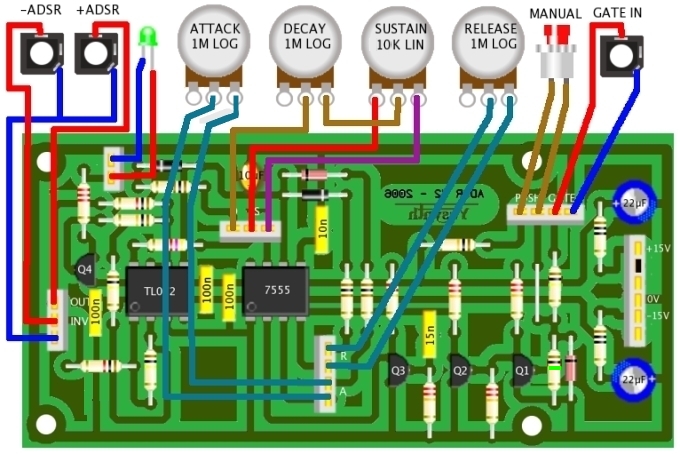

| Wiring |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

Settings and trimming

|

| This circuit does not require any trimming. |

|

|

Références |

|

|

|

|

| Name

: Czaba ZVEKAN Modular project : Location : Basel, Switzerland Website : |

Name

: Etaoin Modular project : Casia MS01 Location : Utrecht, Netherlands Website :www.casia.org/modular |

|

|

|

|

| Name

: Jordi Pseudo : vcfool Modular project : Location : Website : |

Name

: Pseudo : Sebo Modular project : Location : Argentina Website : www.cosaquitosenglobo.com.ar |

Name

: Doug Slocum Pseudo : Modular project : SteamPunk Location : USA Website : www.dougslocum.com |

|

|

|

| Name

: Frédéric Monti Pseudo : zarko Modular project : Location : Gardanne, France Website : |

Name

: Pseudo : Tudy Modular project : Yusynth 17U Location : Brno, Czech Republic Website :www.insania.freemusic.cz |

Name

:

Torsten Pseudo : fogman Modular project : schranzknecht Location : Germany Website : www.vulkanware.de/diy |

|

|||

|

|